为超前进位加法器了实现多位超前进位加法器的二进制数运算超前进位加法器,我们需要将全加器进行级联级联的方式有两种串联行波进位加法器和并联超前进位加法器串联行波进位加法器在串联方式中超前进位加法器,每一个全加器的进位输出都作为下一个全加器的进位输入这种方式的逻辑过程类似于我们列竖式进行加法运算,每一位的加法过程需要等待。

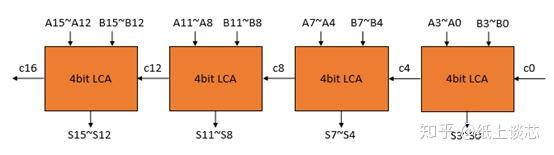

因此通常的实现方法, 是采用多个小规模的超前进位加法器拼接而成一个较大的加法器,例如,用4个8bit的超前进位加法器连接成32bit加法器。

串行加法进位从最低位进到最高位,即整个进位是分若干步骤进行的优点 ,电路结构简单缺点,运算速度慢超前进位的所有位数进位是同时完成的一个CP脉冲就能完成整个进位过程优点,运算速度快,缺点,电路复杂 本回答由提问者推荐 举报 评论 24 5 沉睡的月光 采纳率60% 来自团队喜欢教物理 擅长 工程。

电路图根据逻辑表达式,可以画出一位全加器的电路图电路图由两个二输入异或门两个二输入与门和一个二输入或门构成三多位加法器与超前进位加法器 多个一位全加器可以串行连接,构成多位串行加法器然而,串行加法器的计算速度较慢,因为每一位的计算都依赖于前一位的结果为了提高计算速度。

在探讨超前进位加法器Lookahead Carry Adder, LCA之前,我们先来剖析一下行波进位加法器RCA的关键路径行波进位加法器通过N个全加器级联而成,其性能受制于关键路径,即从输入数据到输出数据完成所需的最长路径在N比特行波进位加法器中,由全加器级联形成的关键路径包括从输入a,b,cin到输出。

超前进位加法器与串行进位加法器是两种常见的加法器实现方式相比于串行进位加法器,超前进位加法器在实现相同精度的条件下,有更快的运算速度和更低的硬件成本这是因超前进位加法器采用预先生成进位信号的方法,避免串行进位加法器中进位信号需要等待前一位计算结果的情况超前进位加法器能够更快地完成。

Ling型加法器是CLA的一种变体,旨在减少硬件开销通过替换某些进位信号,Ling型加法器简化了CLA的实现,使得硬件设计更为紧凑这些设计激发了许多其超前进位加法器他相关研究,包括使用特定技术优化进位网络并行前缀进位加法器PPA利用并行处理技术加速进位计算过程通过合并相邻或重叠的加法器块,并利用特定运算符“。

超前进位加法器比串行进位加法器速度慢的原因是它需要计算两个操作数的相加结果根据公开相关信息显示,根据相加结果来进行进位操作,这个过程需要2个或更多的周期来完成,使得超前进位加法器的运行速度相对较慢,而串行进位加法器只需要一个周期,因此串行进位加法器速度更快。

组合逻辑电路包括半加器全加器加法器四位串行加法器超前进位加法器1半加器两个数AB相加,只求本位之和,暂不管低位送来的进位数,称之为quot半加quot完成半加功能的逻辑电路叫半加器实际作二进制加法时,两个加数一般都不会是一位,因而不考虑低位进位的半加器是不能解决问题的。

低于8倍无法支撑在进行层次化超前类别的进位加法器实验时,低于8倍的门延迟会直接导致计划失败,因此必须要8倍的门延迟才可支撑先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

全加器要逐级传递进位信号全加器中的进位信号要逐级传递,每个全加器的进位信号取决于前一位的进位信号和当前位的输入信号这是全加器是通过门电路实现的,每个门电路的输出信号会受到前一级的进位信号和当前级的输入信号的影响,进位信号要逐级传递全。

数字IC逻辑主要分为四类核心结构组合逻辑时序逻辑状态机逻辑和算术逻辑1 组合逻辑 由基本逻辑门电路构成,输出仅与当前输入相关典型应用包括 bull加法器实现二进制加减运算,如全加器超前进位加法器 bull编码器译码器完成二进制代码转换如8线3线优先编码器 bull。

利用两块四位二进制超前进位全加器74LS283与非门电路74LS00,74LS20构成一位二十进制全加器,即可实现两个8位二进制。

通过使用超前进位技术,可以一次性将所有可能的进位情况表示出来,提高加法运算的效率例如,在计算最高位时,可能需要等待前几个延迟过程完成,以确保所有可能的进位情况都被考虑到半加器和全加器的使用半加器用于处理不考虑进位的情况,即只进行两个一位二进制数的加法运算全加器在半加器。

多位加法器主要分为以下两类串行进位加法器工作原理逐位进行加法运算,每个位的和需要等待下一位的进位信号性能特点运算速度相对较慢,结构简单,适合位数较少的计算超前进位加法器工作原理能够直接计算出每一位的进位输入,无需逐位传递进位性能特点运算速度快,特别是在处理大量数据。

HDL系列BrentKung树形加法器原理与设计 在超前进位加法器中,进位并行计算特性打破了当前进位依赖于前一级进位的传统关系,使得第n位进位与输入直接关联然而,对于位宽较大的加法器,进位生成的逻辑面积增加,导致芯片成本上升研究者们致力于平衡时间延迟与逻辑门数,而较少关注如何通过简洁规则的。

相关标签 :

上一篇: qemu,qemu是什么意思

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com