异步FIFOFirst In First Out在设计中需要处理跨时钟域的数据传输异步fifo,特别是当读写时钟频率相差较大时异步fifo,会出现一些问题,尤其是慢时钟域采样快时钟域数据时可能产生的漏采现象一问题描述 在异步FIFO中,写时钟域快时钟域的write_pointer以较高的频率增加,而读时钟域慢时钟域的read_pointer则以较。

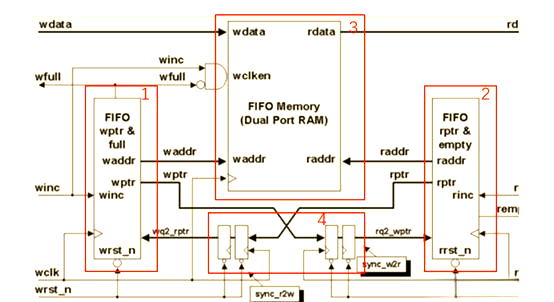

异步FIFO浅析FIFOFirst in First out即先进先出数据缓存器,与普通存储器的区别在于没有外部读写的地址线,只能顺序地读取和写入数据按读写是否为相同时钟域,FIFO可分为同步和异步两种,其中异步FIFO主要用于跨时钟域传输数据一异步FIFO的基本结构异步FIFO主要包含以下五个模块FIFO的基本存储单。

由于漏采现象和跨时钟域信号同步问题的存在,异步FIFO在读写时钟相差太大的情况下,其效率会受到影响系统可能需要增加额外的等待时间或采取其异步fifo他措施来确保数据的正确传输和存储,这些都会降低FIFO的整体效率因此,在设计异步FIFO时,需要充分考虑读写时钟的差异,并采取相应的措施来避免或减轻上述问题,以。

在异步FIFOFirst In First Out的设计中,空满信号的判断是至关重要的,因为它们直接关系到FIFO能否正确地进行读写操作而不发生数据溢出或读取无效数据以下是对异步FIFO读写中空满现象的详细解释一空满信号的重要性FIFO中的空满信号用于指示FIFO的当前状态,以便控制系统在适当的时候进行读写操作。

1 类型深度与数据位宽设定 选择 DCFIFO确保选择的是异步 FIFO进行配置 数据位宽匹配输入与输出数据位宽需满足2n的倍数关系,以兼容不同频率的输入输出若输入与输出数据位宽不同,应勾选“Use a different output width”并填写相应的输出数据位宽2 数据输出顺序 正常模式输出数据滞后。

基于FPGA的异步FIFO设计与实现 在FPGA设计中,异步FIFOFirstIn FirstOut是一种重要的存储结构,用于在不同时钟域之间传输数据以下是对基于FPGA的异步FIFO设计及其实现的详细解释一异步FIFO的基本原理 FIFO的定义FIFO是一种先进先出的存储结构,按照数据写入的顺序往外读出数据异步FIFO的特点。

同步FIFO和异步FIFO总结如下一同步FIFO 定义使用同一时钟进行读写操作的FIFO 特点 时钟同步读写操作在同一时钟域下进行,简化了设计 空满检测通过data_count和指针对比来判断FIFO的空满状态 应用场景适用于同一时钟域内的数据缓冲二异步FIFO 定义适用于不同时钟域间通信。

异步FIFO复位有同步复位和异步复位两种方式,其复位顺序和要求如下同步复位由于复位信号已经是同步的,因此无需设计额外的同步逻辑,按正常同步逻辑进行复位操作即可异步复位复位条件复位必须在所有时钟有效时进行,否则FIFO的状态无法预测复位信号脉宽复位信号的脉宽至少为3个慢时钟周期避免读写操作。

异步FIFO的实现涉及多个关键步骤,从Verilog代码设计到波形验证,以下是详细解答一Verilog代码设计 双端口RAM设计核心组件双端口RAM是异步FIFO的核心存储单元接口信号包括写时钟写复位写使能写地址写数据,以及对应的读信号RAM深度与地址宽度通过参数RAM_DEPTH定义RAM的深度,与地址宽度。

同步FIFO只有一个独立的时钟端口clock,所有的输入输出信号都同步于clock信号异步FIFO有两个时钟,写端口和读端口分别有独立的时钟所有写相关的信号都属于写时钟,所有与读相关的信号都属于读时钟三FIFO IP 在FPGA设计中,FIFO一般不需要自己去写代码实现,因为FPGA官方软件都提供了FIFO IP。

异步FIFO读写时钟相差太大可能会导致漏采现象空满信号判断不准确以及亚稳态问题一漏采现象 当读时钟RDCLK和写时钟WRCLK差距较大时,慢时钟域在采样快时钟域的数据时可能会出现漏采这种情况虽然不会导致功能错误,但会使空满信号的判断变得更为保守,降低效率同时,由于漏采,快时钟域的读写指针在同步。

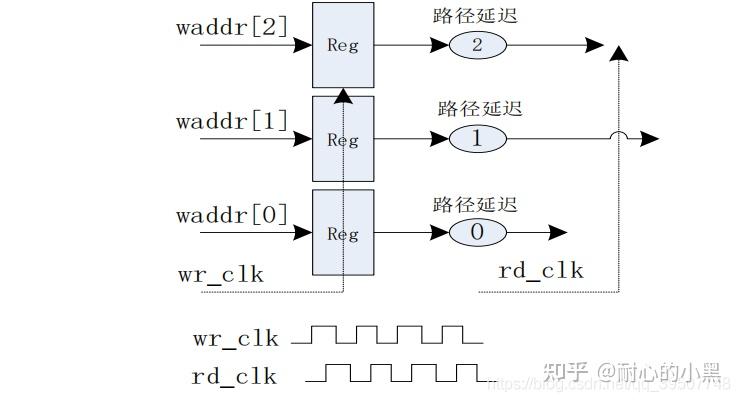

用FPGA和格雷码实现异步FIFO的关键点如下格雷码的应用格雷码适用于连续变化的信号,特别是在跨时钟域同步时,由于其一次只有一位信号反转变化,因此能有效降低同步的难度在异步FIFO中,格雷码主要用于同步读写地址信号,以减少同步过程中的亚稳态问题异步FIFO的接口异步FIFO的接口包括读写时钟信号。

异步FIFO的空满检测是通过比较读写地址进行满空判断,但是读写地址属于不同的时钟域,所以在比较之前需要先将读写地址进行同步处理,此机制保证了FIFO在空满极限情况下,依然留有余量,存在一定的冗余空间,以防写满溢出,读空多读的情况无论是wclk和rclk谁快谁慢,都可能产生假空假满现象,但是。

当异步FIFO的深度不是2的n次方时,会出现地址回绕问题和空满判断复杂的问题,需要采取特定的设计策略来处理地址回绕问题当FIFO深度不是2的n次方时,地址从最大值回绕到最小值时,会有多个比特位同时变化这增加了跨时钟域传输时的亚稳态风险,因为多个比特位的同时变化可能导致接收端无法稳定地。

FPGA调试FIFO时可能会遇到的坑主要包括复位信号问题数据错位和缺失异步FIFO的读写计数不准以及FIFO写不进去数据等1 复位信号问题 复位信号的使用不当可能导致FIFO无法正常工作例如,复位信号的有效长度不够,可能导致FIFO没有正确初始化,从而无法写入数据复位信号在读取操作进行时被触发,也可能。

异步FIFO的简单介绍中,FIFO的基本结构可以通过DPRRAM实现,但与普通存储器不同的是,FIFO遵循先进先出的原则,不需要地址在牛客网等平台刷题有助于提升编程技能,了解FIFO编程题目,详细解题思路和答案解析可以增强学习效果在设计异步FIFO时,首先要理解同步和异步的区别同步时序逻辑基于同一时钟信号。

文章总结FIFO,即先进先出缓冲器,是数据处理中常见的存储器类型,其主要作用是数据缓冲和时钟域隔离同步FIFO和异步FIFO的主要区别在于读写时钟的同步性同步FIFO使用同一时钟进行读写操作,而异步FIFO适用于不同时钟域间的通信,通过格雷码同步减少亚稳态问题在设计FIFO时,关键在于空满状态的检测。

相关标签 :

上一篇: 人脸识别SDK,人脸识别SDK包天津地铁

微信医疗(登记+咨询+回访)预约管理系统

微信医疗(登记+咨询+回访)预约管理系统  云约CRM微信小程序APP系统定制开发

云约CRM微信小程序APP系统定制开发  云约CRM体检自定义出号预约管理系统

云约CRM体检自定义出号预约管理系统  云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统

云约CRM云诊所系统,云门诊,医疗预约音视频在线问诊预约系统  云约CRM新版美容微信预约系统门店版_门店预约管理系统

云约CRM新版美容微信预约系统门店版_门店预约管理系统 云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统

云约CRM最新ThinkPHP6通用行业的预约小程序(诊所挂号)系统联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com