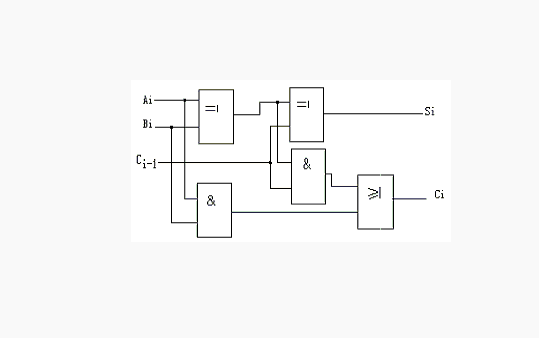

1、C 等于 XYZ=11 时,C 等于 14 画出逻辑图根据前面一位全加器逻辑电路图的分析,除了 74LS153,还需要一个非门用 153 设计电路,在分析各个输入端是什么信号时,只需使用真值表由于不是用逻辑门设计电路,卡诺图逻辑表达式,就都是不需要的有人,列出了“全加器的逻辑表达式”,明显是冒充内行用一位全加器逻辑电路图;单用一片74HC138无法实现全加器功能,还要加一片双通道的4输入与非门74HC20实用电路如下图这个电路的设计目的是为了实现全加器的功能全加器是一种数字电路,用于将两个位以及来自低位的进位位进行相加因此,它需要能够处理两个输入位和一个进位输入,同时产生一个和位和一个新的进位一位全加器逻辑电路图;或门的输出作为加法器的进位输出即完成了加法器的设计回过头来分析当加法器的输入分别为a=1,b=0,ci=1时对应38译码器的输入为A=1,B=0,C=1,这是译码器对应的输出为OUT5=1,其余的为0,根据上面设计的连接关系,s=0,co=1,满足全加器的功能,举其一位全加器逻辑电路图他的例子也一样,所以,设计;否则,输出为低电平通过这些逻辑门的组合,可以实现全加器的复杂逻辑功能全加器的逻辑图如下所示首先,将A和B输入信号分别与进位信号Ci进行异或运算,得到两个部分和信号然后,将这两个部分和信号进行与非运算,得到最终的输出信号S这样的设计不仅简化了电路结构,还提高了运算效率。

2、无法用与或非门设计一位全加器,因为一位全加器是用门电路实现两个二进制数相加并求出和的组合线路它只能利用门电路实现,而无法用与或非门实现;在其它位,都是三个一位数相加,同样会产生 C进位以及 S和三个一位数相加,这就必须用“全加器”完成了它们的真值表以及逻辑表达式,在图中,都已给出它们的逻辑电路图,当然也可以用“门电路”组成但是,半加器全加器,都有自己的逻辑符号再用“门电路”来画电路图,就有。

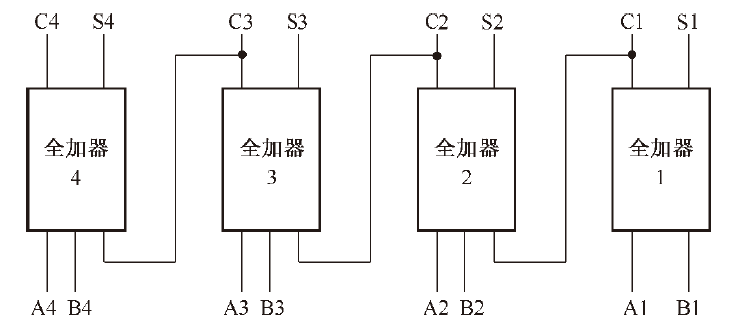

3、用于门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器一位全加器可以处理低位进位,并输出本位加法进位多个一位全加器进行级联可以得到多位全加器常用二进制四位全加器74LS283提供与非门的是74LS86,有4个与非门;电路图加法器是一种电子运算器,用于将两个二进制数相加它是计算机和其一位全加器逻辑电路图他数字系统中常用的基本元件之一加法器可以执行各种算术运算,包括加法减法乘法和除法等加法器的基本原理是将两个二进制数的每一位相加,并产生相应的和如果两个数的某一位的和大于1,则会产生进位信号,并将该信号;当M=1时,加法器成为减法器,M=1与B进行按位亦或操作,相当于对B进行位取反,然后C0=M=1作为加数进入首个全加器,这是计算机二进制减法常用的方法,一个负数表示成补码形式与另一个数相加,相当于用那个数减去它这里的M执行了求补码的操作,按位取反并加1因此当M=1时,这个图变成减法器;2D0=0,2D3=1,2D1=2D2=C0,1Q=S1,2Q=C1根据对应的管脚连接电路在其它位,都是三个一位数相加,同样会产生C进位以及S和三个一位数相加,这就必须用“全加器”完成了它们的真值表以及逻辑表达式,在图中,都已给出它们的逻辑电路图,当然也可以用“门电路”组成;全加器逻辑图原理 两个多位二进制数相加时,除了最低位以外,其他每一位相加时都需要考虑低位的进位,即将加数被加数和低位的进位3个数相加,这种加法运算称为全加运算,实现全加运算的电路叫做全加器全加器工作原理 英语名称为fulladder,是用门电路实现两个二进制数相加并求出和的组合线路,称;Multisim是一款专门用于电路设计与仿真的软件工具,能够帮助工程师进行电路设计和仿真一位全加器的实现过程涉及多个步骤首先,需要确定输入信号AB和Cin,以及输出信号S和Co接下来,根据逻辑表达式设计电路图,具体可以使用逻辑门译码器和数据选择器等元件此外,还可以利用Multisim软件进行仿真,确保;一位全加器AB为加数,C为前进位,S为和,Co为后进位ABC分别为74LS138的数据输入位,Y为74LS138的输出位真值表如下图示那么把 S=1 的 Y 端通过四输入与非门连接在一起,则门输出即为 S把 C0=1 的 Y 端通过四输入与非门连接在一起,则门输出即为 Co。

4、并行进位公式并行加法器使用并行进位公式来计算每一位的进位输出这些公式基于二进制加法的规则,通过逻辑推导得到工作原理在并行加法器中,所有位的进位输出都是同时计算的,因此可以大大提高加法运算的速度这是通过在ALU内部设置复杂的逻辑电路来实现的,这些电路能够根据操作数和运算类型快速计算出;74LS00和74LS86画出一位全加器,化简的逻辑函数如下 根据这个函数画出逻辑图如下。

相关标签 :

上一篇: 照片书怎么做,照片书制作模板

下一篇: 免费ss,免费ssl证书永久生成

windowsxp系统修复,winxp系统修复命令具体操作

windowsxp系统修复,winxp系统修复命令具体操作 空间音乐播放器代码,空间音乐播放器代码是什么

空间音乐播放器代码,空间音乐播放器代码是什么 专注于win7,专注于win7唯一官网

专注于win7,专注于win7唯一官网 microsoft.netframework是什么,microsoft net framework在哪里

microsoft.netframework是什么,microsoft net framework在哪里 文件夹exe病毒专杀,电脑文件夹exe病毒专杀

文件夹exe病毒专杀,电脑文件夹exe病毒专杀 ipad24.3.5越狱,ipad935为什么升不了级

ipad24.3.5越狱,ipad935为什么升不了级联系电话:18300931024

在线QQ客服:616139763

官方微信:18300931024

官方邮箱: 616139763@qq.com